Why would you need a heterogeneous multicore processing architecture?

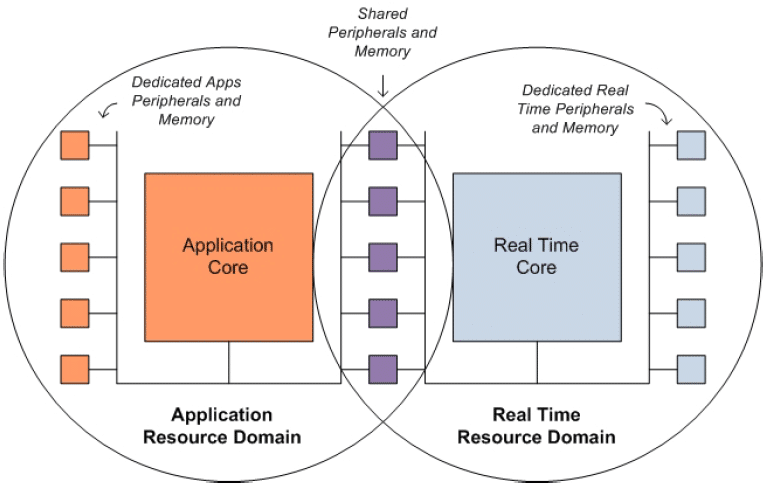

Nowadays people look to achieve high-performance processing and low power requirements for their IoT solutions devices. They also look for a high degree of functional integration and want to perform complex operations with them. All these products are targeted towards a growing market of connected and portable devices that run user-friendly applications. To take advantage of these devices, it is necessary to have some type of Operating System (OS) to help run applications that benefit the end user to interact with the device. A processor containing a heterogeneous multicore processing architecture (several CPU cores and a special purpose processor) will help to have more flexibility while working with advanced embedded systems.

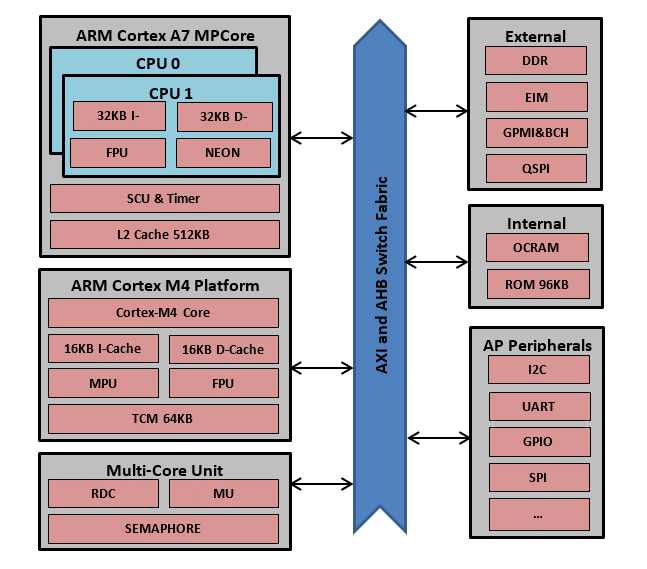

The NXP i.MX 7 processor, for example, includes an ARM Cortex-A7 (one or two cores) plus one ARM Cortex-M4 core, providing the chance to run an OS like Linux on the Cortex-A7 core and a real-time OS like FreeRTOS on the Cortex-M4. Running Linux helps communicate all the different features required for our device and running FreeRTOS will take care of the real-time capabilities required.

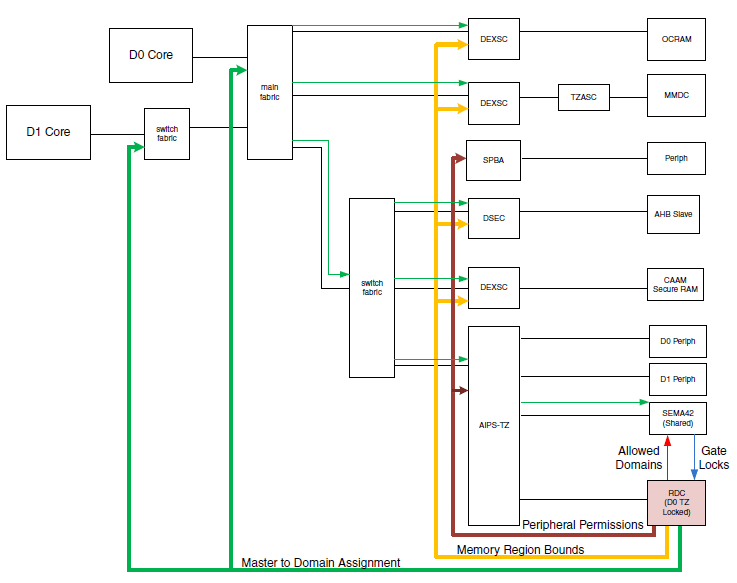

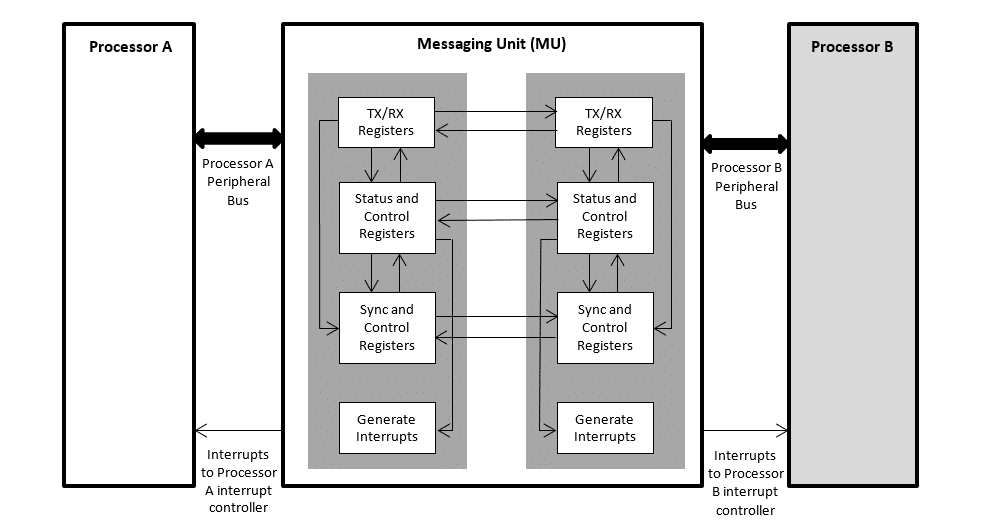

This article gives an overview of how to take advantage of a heterogeneous multicore processing architecture (i.MX7), how the communication between the different modules can be managed and all the components involved.